Difference between revisions of "IGEP Technology devices revisions"

From IGEP - ISEE Wiki

m (→IGEP Processor Boards) |

(→IGEP Processor Boards) |

||

| (One intermediate revision by the same user not shown) | |||

| Line 14: | Line 14: | ||

<section end=Codeformat/> | <section end=Codeformat/> | ||

| − | == IGEP Processor Boards == | + | ==IGEP Processor Boards== |

| + | {{Category:IGEP0010|IGEP0010 revisions}} | ||

| − | {{ | + | {{Category:IGEP0020|IGEP0020 revisions}} |

| − | {{ | + | {{Category:IGEP0030|IGEP0030 revisions}} |

| − | {{ | + | {{Category:IGEP0032|IGEP0032 revisions}} |

| − | |||

| − | |||

== IGEP Expansion Boards == | == IGEP Expansion Boards == | ||

Latest revision as of 20:28, 14 November 2017

Contents

Every IGEP device has a Item Code like XXXX8888-RvMm

That means several information about:

- XXXX8888: Project codename

- -R: (no information, just format)

- v: Version of PCB

- M: Model of assembled product (for example: WIFI model or NO WIFI model)

- m: manufacturing revision

This IGEP Technology devices revisions article gives a list of Item Codes of IGEP Devices.

IGEP Processor Boards

IGEP0010 revisions

| Revision | Name | Comments |

| IGEP0010-RA | IGEP0010 | All IGEPv1 boards are based on ARM9 processor. Boards for very cheap custom designs under project agreement. |

IGEP0020 revisions

| Revision | Name | Comments |

| IGEP0020-RA | IGEPv2 | Not for general public. Only few Premium customers have this board revision |

| IGEP0020-RB1 | IGEPv2 | These boards are made from the year 2009 to 2010. They are not available anymore (see IGEP0020-RC3 below) |

| IGEP0020-RCX | IGEPv2 | These boards are made from the year 2010 to 2011 |

| IGEP0020-RC1 | IGEPv2 | These boards are marked with "1" hand-made number on silkscreen box of IGEP0020-RC.

These boards are shipped with OMAP3530 and wireless. MODEL: IGEP0020-RC1-OMAP3530-720Mhz |

| IGEP0020-RC2 | IGEPv2 | These boards are marked with "2" hand-made number on silkscreen box of IGEP0020-RC.

These boards are shipped with OMAP3530 and without wireless. MODEL: IGEP0020-RC2-OMAP3530-720Mhz-NOWIFI |

| IGEP0020-RC3 | IGEPv2 | These boards are marked with "3" hand-made number on silkscreen box of IGEP0020-RC.

These boards are shipped with OMAP3530 and wireless with IGEP0020-RB1 backward compatibility. They are for customers who need IGEP0020RB1 boards. |

| IGEP0020-RC4 | IGEPv2 | These boards are marked with "4" hand-made number on silkscreen box of IGEP0020-RC.

These boards are shipped with DM3730 and wireless. MODEL: IGEP0020-RC4-DM3730-1GHz |

| IGEP0020-RC5 | IGEPv2 | These boards are marked with "5" hand-made number on silkscreen box of IGEP0020-RC.

These boards are shipped with DM3730 and without wireless. MODEL: IGEP0020-RC5-DM3730-1GHz-NOWIFI |

| IGEP0020-RC6 | IGEPv2 | These boards are marked with "6" hand-made number on silkscreen box of IGEP0020-RC (before 2012 year) or Datamatrix code label "IGEP0020-RC6" (2012 and later).

These boards are shipped with DM3730 and wireless, but they ship NANDFlash memory. |

| IGEP0020-RC61 | IGEPv2 | These boards are marked with Datamatrix code label "IGEP0020-RC6x"

These boards are like IGEP0020-RC6 plus manufacturing improvements and solve hardware bugs. |

| IGEP0020-RC7 | IGEPv2 | These boards are marked with "7" hand-made number on silkscreen box of IGEP0020-RC (before 2012 year) or Datamatrix code label "IGEP0020-RC7" (2012 and later).

These boards are shipped with DM3730 and without wireless, but they ship NANDFlash memory. |

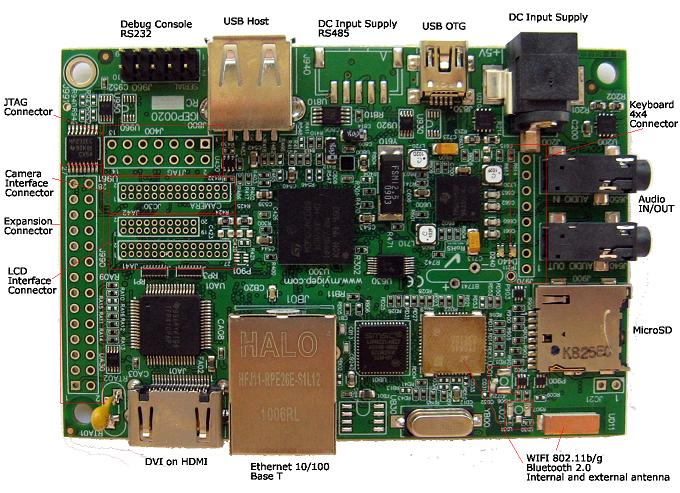

IGEP0020 expansion connectors

|

J990 connector

Using this expansion connector you have access to McBSP1, McBSP3, I2C2, MMC2(8 bits), nReset and REGEN signals from OMAP Processor. The interface is at 1.8V on all signals. Only 1.8V CMOS levels are supported. Do not expose the header to 3.3V.

J990 connector is BeagleBoard compatible expansion connector. IGEPv2-NOWIFI board is fully compatible. Other IGEPv2 board versions need software configuration to disable wifi interface and others because of shared hardware lines. MMC2 interface is used by wifi module. McBSP3 interface is used by PCM TPS65950 interface.

See which versions have WIFI/BT combo available.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | VIO 1V8 | - | Power 1v8 | - | - |

| 2 | DC 5V | - | Power 5v | - | - |

| 3 | MMC2_DAT7 | GPIO_139(mode=4) | Reset WIFI |

MMC2_DAT7(mode=0) |

WIFI/BT combo:WIFI |

| 5 | MMC2_DAT6 | GPIO_138(mode=4) | Power down WIFI |

MMC2_DAT6(mode=0) |

WIFI/BT combo:WIFI |

| 7 | MMC2_DAT5 | GPIO_137(mode=4) | Reset BT |

MMC2_DAT5(mode=0) |

WIFI/BT combo:BT |

| 9 | MMC2_DAT4 | GPIO136(mode=4) | - |

MMC2_DAT4(mode=0) |

- |

| 11 | MMC2_DAT3 | MMC2_DAT3(mode=0) | Transfer data |

McSPI3_CS0(mode=1) |

WIFI/BT combo:WIFI |

| 13 | MMC2_DAT2 | MMC2_DAT2(mode=0) | Transfer data |

McSPI3_CS1(mode=1) |

WIFI/BT combo:WIFI |

| 15 | MMC2_DAT1 | MMC2_DAT1(mode=0) | Transfer data | GPIO_133(mode=4) SAFE_MODE(mode=7) |

WIFI/BT combo:WIFI |

| 17 | MMC2_DAT0 | MMC2_DAT0(mode=0) | Transfer data |

McSPI3_SOMI(mode=1) |

WIFI/BT combo:WIFI |

| 19 | MMC2_CMD | MMC2_CMD(mode=0) | Control Wire for bus MMC2 (WIFI) |

McSPI3_SIMO(mode=1) |

WIFI/BT combo:WIFI |

| 21 | MMC2_CLK0 | MMC2_CLK(mode=0) | Clock for MMC2 (WIFI) |

McSPI3_CLK(mode=1) |

WIFI/BT combo:WIFI |

| 4 | MCBSP3_DX | MCBSP3_DX (mode=0) | Transmitted serial Data (BT audio) |

UART2_CTS(mode=1) |

TPS65950: PCM VSP |

| 6 | MCBSP3_CLKX | MCBSP3_CLKX(mode=0) | Transmitted serial Clock (BT audio) |

UART2_TX(mode=1) |

BT/TPS65950: PCM VSP |

| 8 | MCBSP3_FSX | MCBSP3_FSX (mode=0) | Transmited Frame Syncronisation (BT audio) |

UART2_RX(mode=1) |

BT/TPS65950: PCM VSP |

| 10 | MCBSP3_DR | MCBSP3_DR (mode=0) | Received Serial Data (BT audio) | UART2_RTS(mode=1) GPIO_141(mode=4) HSUSB3_TLL_D5(mode=5) SAFE_MODE(mode=7) |

TPS65950: PCM VSP |

| 12 | MCBSP1_DX | GPIO_158(mode=4) | - | MCBSP1_DX(mode=0) McSPI4_SIMO(mode=1) McBSP3_DX(mode=2) SAFE_MODE(mode=7) |

- |

| 14 | MCBSP1_CLKX | GPIO_162(mode=4) | - | MCBSP1_CLKX(mode=0) McBSP3_CLKX(mode=2) SAFE_MODE(mode=7) |

- |

| 16 | MCBSP1_FSX | GPIO_161(mode=4) | - | MCBSP1_FSX(mode=0) McSPI4_CS0(mode=1) McBSP3_FSX(mode=2) SAFE_MODE(mode=7) |

- |

| 18 | MCBSP1_DR | GPIO_159(mode=4) | - | MCBSP1_DR(mode=0) McSPI4_SOMI(mode=1) McBSP3_DR(mode=2) SAFE_MODE(mode=7) |

- |

| 20 | MCBSP1_CLKR | GPIO_156(mode=4) | - | MCBSP1_CLKR(mode=0) MCSPI4_CLK(mode=1) SAFE_MODE(mode=7) |

- |

| 22 | MCBSP1_FSR | GPIO_157(mode=4) | - | MCBSP1_FSR(mode=0) CAM_GLOBAL_RESET(mode=2) SAFE_MODE(mode=7) |

- |

| 23 | I2C2_SDA | I2C2_SDA(mode=0) | I2C2 Data | GPIO_183(mode=4) SAFE_MODE(mode=7) |

CAM if configured via hardware: RC14 |

| 24 | I2C2_SCL | I2C2_SCL(mode=0) | I2C2 Clock | GPIO_168(mode=4) SAFE_MODE(mode=7) |

CAM if configured via hardware: RC13 |

| 25 | REGEN | - | Master/Slave control power TPS65950 | - | - |

| 26 | nRESET | - | Read Reset Omap | - | - |

| 27 | GND | - | GND | - | - |

| 28 | GND | - | GND | - | - |

J960 connector

This connector is used mainly to connect via serie to IGEP Software using RS232 standard.

On IGEPv2 revision B:

- This J960 connector has only Debug RS232 interface

- So, it is needed null modem configuration (direct connection between two computers). RX and TX lines are crossed in this null modem configuration between two equipments (TX1->RX2 / TX2->RX1).

On IGEPv2 revision C:

- You should modify your serial debug cable in order not to damage your serial PC port.

- Additional RS232 port (UART1) on same J960 connector. It is only needed to rotate 180o the IDC-10 (AT-Everex) to DB9 cable.

- It has been added resistors for alternative UART1, UART2 and UART3 hardware selection.

- See Schematics (RC) for more information.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals (only via hardware) |

Share with |

| 1 | - | - | - | - | - |

| 2 | RS232_RX2 | UART3_RX(R966) | Serial debug | UART2_RX(R952) only RC | SN65C3232EPW |

| 3 | RS232_TX2 | UART3_TX(R965) | Serial debug | UART2_TX(R947) only RC | SN65C3232EPW |

| 4 | - | - | - | - | - |

| 5 | GND | - | GND | - | - |

| 6 | GND | - | GND | - | - |

| 7 | - | - | - | - | - |

| 8 | RS232_TX1 | UART1_TX(R961) | - | UART3_TX(R940) only RC | SN65C3232EPW |

| 9 | RS232_RX1 | UART1_RX(R962) | - | UART3_RX(R942) only RC | SN65C3232EPW |

| 10 | - | - | - | - | - |

SN65C3232EPW: IC RS232 LINE DVR/RCVR

J940 connector

This connector is used mainly to connect via RS485 (UART1) with other devices. User can use this connector to power the board with 5VDC. Use only 5V regulated DC. The IGEPv2 BOARD does not use this 9v power supply. Only on IGEPv2 revision B, the PWR_9V input is directly routed to JC01 and J971 connectors. On IGEPv2 revision C is not available.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | PWR_GND | GND | - | - | - |

| 2 | PWR_5V | Power 5v | - | - | - |

| 3 | PWR_9V | (Not connected) | - | - | - |

| 4 | RS485_A | UART3_RX/UART3_TX | A aka '−' aka TxD-/RxD- aka inverting pin | - | TXS0102DCUR |

| 5 | RS485_B | UART3_RX/UART3_TX | B aka '+' aka TxD+/RxD+ aka non-inverting pin | - | TXS0102DCUR |

TXS0102DCUR: Bidirectional voltage-level translator

J400 connector

J400 is used to JTAG (Joint Test Action Group). JTAG is a standardized serial protocol widely used in printed circuit boards. Its main functions are:

- Debug the software of an embedded system directly

- Storing firmware

- Boundary scan testing

JTAG Suggested:

- JTAG Debugger XDS510+ USB from Spectrum Digital with Code Composer Studio 3.3 or higher.

- JTAG Debugger XD100v2 USB from Spectrum Digital with Code Composer Studio 4 or higher.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | JTAG_TMS | JTAG_TMS | |

- | - |

| 2 | JTAG_NTRST | JTAG_NTRST | - | - | |

| 3 | JTAG_TDI | JTAG_TDI | |

- | - |

| 4 | GND | - | GND | - | - |

| 5 | 1V8 | Power 1V8 | |

- | - |

| 6 | - | - | - | - | |

| 7 | JTAG_TD0 | JTAG_TD0 | |

- | - |

| 8 | GND | - | GND | - | - |

| 9 | JTAG_RTCK | JTAG_RTCK | |

- | - |

| 10 | GND | - | GND | - | - |

| 11 | JTAG_TCK | JTAG_TCK | |

- | - |

| 12 | GND | - | GND | - | - |

| 13 | JTAG_EMU0 | JTAG_EMU0(mode=0) | |

GPIO_11(mode=4) SAFE_MODE(mode=7) |

- |

| 14 | JTAG_EMU1 | JTAG_EMU1(mode=0) | GPIO_31(mode=4) SAFE_MODE(mode=7) |

- |

J970 connector

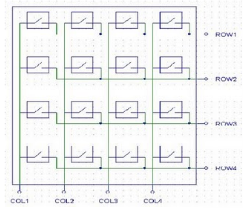

J970 is used to implement a keypad, it is connected to TPS65950. The keypad interface controller provides an enhanced keypad decode capability and simultaneously reduces host processor software overhead. When a key button of the keyboard matrix is pressed the corresponding row and column lines are shorted together. To allow key press detection, all input pins (KBR) are pulled up to VCC and all output pins (KBC) driven to a low level. Any action on a button generates an interrupt to the sequencer. The decoding sequence is written to allow detection of simultaneous press actions on several key buttons.

More information in TPS65950 datasheets. TPS65950 send via I2C1 all the interrupt request.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | KPD_CO | KPD_CO | Keypad controler Column 0 | - | - |

| 2 | KPD_C1 | KPD_C1 | Keypad controler Column 1 | - | - |

| 3 | KPD_C2 | KPD_C2 | Keypad controler Column 2 | - | - |

| 4 | KPD_C3 | KPD_C3 | Keypad controler Column 3 | - | - |

| 5 | KPD_RO | KPD_RO | Keypad controler Row 0 | - | - |

| 6 | KPD_R1 | KPD_R1 | Keypad controler Row 1 | - | - |

| 7 | KPD_R2 | KPD_R2 | Keypad controler Row 2 | - | - |

| 8 | KPD_R3 | KPD_R3 | Keypad controler Row 3 | - | - |

JC30 connector

These connectors allow the access to the Camera interface signals. Omap has the processing capability to connect RAW image-sensor modules via this connector.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | CAM_HS | GPIO_94(mode=4) | - | CAM_HS(mode=0) HW_DBG0(mode=5) SAFE_MODE(mode=7) |

- |

| 2 | CAM_VS | GPIO_95(mode=4) | - | CAM_VS(mode=0) HW_DBG1(mode=5) SAFE_MODE(mode=7) |

- |

| 3 | CAM_XCLKA | CAM_XCLKA(mode=0) | Camera interface | GPIO_96(mode=4) SAFE_MODE(mode=7) |

- |

| 4 | GND | - | GND | - | - |

| 5 | CAM_PCLK | CAM_PCLK(mode=0) | Camera interface | GPIO_97(mode=4) HW_DBG2(mode=5) SAFE_MODE(mode=7) |

- |

| 6 | GND | - | GND | - | - |

| 7 | CAM_DO | GPIO_99(mode=4) | - | CAM_DO(mode=0) SAFE_MODE(mode=7) |

- |

| 8 | CAM_FLD | GPIO_98(mode=4) | - | CAM_FLD(mode=0) CAM_GLOBAL_RESET(mode=2) HW_DBG3(mode=5) SAFE_MODE(mode=7) |

- |

| 9 | CAM_D2 | CAM_D2(mode=0) | Camera interface | GPIO_101(mode=4) HW_DBG4(mode=5) SAFE_MODE(mode=7) |

- |

| 10 | CAM_D1 | GPIO_100(mode=4) | - | CAM_D1(mode=0) SAFE_MODE(mode=7) |

- |

| 11 | CAM_D4 | CAM_D4(mode=0) | Camera interface | GPIO_103(mode=4) HW_DBG6(mode=5) SAFE_MODE(mode=7) |

- |

| 12 | CAM_D3 | CAM_D3(mode=0) | Camera interface | GPIO_102(mode=4) HW_DBG5(mode=5) SAFE_MODE(mode=7) |

- |

| 13 | CAM_D6 | GPIO_105(mode=4) | - | CAM-D6(mode=0) SAFE_MODE(mode=7) |

- |

| 14 | CAM_D5 | CAM_D5(mode=0) | Camera interface | GPIO_104(mode=4) HW_DBG7(mode=5) SAFE_MODE(mode=7) |

- |

| 15 | CAM_D8 | GPIO_107(mode=4) | - | CAM_D8(mode=0) SAFE_MODE(mode=7) |

- |

| 16 | CAM_D7 | GPIO_106(mode=4) | - | CAM_D7(mode=0) SAFE_MODE(mode=7) |

- |

| 17 | CAM_D10 | CAM_D10(mode=0) | Camera interface | GPIO_109(mode=4) HW_DBG8(mode=5) SAFE_MODE(mode=7) |

- |

| 18 | CAM_D9 | GPIO_108(mode=4) | - | CAM_D9(mode=0) SAFE_MODE(mode=7) |

- |

| 19 | CAM_XCLKB | CAM_XCLKB(mode=0) | Camera interface | GPIO_111(mode=4) SAFE_MODE(mode=7) |

- |

| 20 | CAM_D11 | CAM_D11(mode=0) | Camera interface | GPIO_110(mode=4) HW_DBG9(mode=5) SAFE_MODE(mode=7) |

- |

| 21 | GPIO_112/I2C2_SCL | GPIO_112(RC11) | - | I2C2_SCL(RC13) SAFE_MODE(mode=7) |

- |

| 22 | GPIO_113/I2C2_SDA | GPIO_113(RC12) | - | I2C2_SDA(RC14) SAFE_MODE(mode=7) |

- |

| 23 | CAM_RESET | GPIO_114(mode=4) | |

SAFE_MODE(mode=7) | - |

| 24 | CAM_PDN | GPIO_115(mode=4) | SAFE_MODE(mode=7) | - | |

| 25 | CAM_STROBE | CAM_STROBE(mode=0) | Camera interface | GPIO_126(mode=4) HW_DBG11(mode=5) SAFE_MODE(mode=7) |

- |

| 26 | CAM_WEN | GPIO_167(mode=4) | - | CAM_WEN(mode=0) CAM_SHUTTER(mode=2) HW_DBG10(mode=5) SAFE_MODE(mode=7) |

- |

| 27 | 3V3 | - | Power 3V3 | - | - |

| 28 | 3V3 | - | Power 3V3 | - | - |

TFT CONNECTORS: JA41-JA42

These connectors allow the access to the LCD signals.The output signal is shared by HDMI-A

JA41 connector

JA41 is used for DVI (Digital Video Interface) data part.

IGEPv2 RB version:

- Available only the first 20 pads

IGEPv2 RC version:

- Available only the first 28 pads

IGEPv2 RG version:

- Available all 30 pads

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | VIO 3V3 | - | Power 3v3 | - | - |

| 2 | GND | - | GND | - | - |

| 3 | DVI_DATA0 | DSS_D0(mode=0) | LCD pixel data bit |

UART1_CTS(mode=2) |

TFP410 |

| 4 | DVI_DATA1 | DSS_D1(mode=0) | LCD pixel data bit |

UART1_RTS(mode=2) |

TFP410 |

| 5 | DVI_DATA2 | DSS_D2(mode=0) | LCD pixel data bit | DSSVENC656_DATA2(mode=3) GPIO_72(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 6 | DVI_DATA3 | DSS_D3(mode=0) | LCD pixel data bit | DSSVENC656_DATA3(mode=3) GPIO_73(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 7 | DVI_DATA4 | DSS_D4(mode=0) | LCD pixel data bit |

DSSVENC656_DATA4(mode=3) |

TFP410 |

| 8 | DVI_DATA5 | DSS_D5(mode=0) | LCD pixel data bit |

DSSVENC656_DATA5(mode=3) |

TFP410 |

| 9 | DVI_DATA6 | DSS_D6(mode=0) | LCD pixel data bit |

DSSVENC656_DATA6(mode=3) |

TFP410 |

| 10 | DVI_DATA7 | DSS_D7(mode=0) | LCD pixel data bit |

DSSVENC656_DATA7(mode=3) |

TFP410 |

| 11 | DVI_DATA8 | DSS_D8(mode=0) | LCD pixel data bit | GPIO_78(mode=4) HW_DBG16(mode=5) SAFE_MODE(mode=7) |

TFP410 |

| 12 | DVI_DATA9 | DSS_D9(mode=0) | LCD pixel data bit | GPIO_79(mode=4) HW_DBG17(mode=5) SAFE_MODE(mode=7) |

TFP410 |

| 13 | DVI_DATA10 | DSS_D10(mode=0) | LCD pixel data bit | GPIO_80(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 14 | DVI_DATA11 | DSS_D11(mode=0) | LCD pixel data bit | GPIO_81(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 15 | DVI_DATA12 | DSS_D12(mode=0) | LCD pixel data bit | GPIO_82(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 16 | DVI_DATA13 | DSS_D13(mode=0) | LCD pixel data bit | GPIO_83(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 17 | DVI_DATA14 | DSS_D14(mode=0) | LCD pixel data bit | GPIO_84(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 18 | DVI_DATA15 | DSS_D15(mode=0) | LCD pixel data bit | GPIO_85(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 19 | DVI_DATA16 | DSS_D16(mode=0) | LCD pixel data bit | GPIO_86(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 20 | DVI_DATA17 | DSS_D17(mode=0) | LCD pixel data bit | GPIO_87(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 21 | DVI_DATA18 | DSS_D18(mode=0) | LCD pixel data bit |

DSS_D0 (mode=3) |

TFP410 |

| 22 | DVI_DATA19 | DSS_D19(mode=0) | LCD pixel data bit |

DSS_1 (mode=3) |

TFP410 |

| 23 | DVI_DATA20 | DSS_D20(mode=0) | LCD pixel data bit |

DSS_D2 (mode=3) |

TFP410 |

| 24 | DVI_DATA21 | DSS_D21(mode=0) | LCD pixel data bit |

DSS_D3 (mode=3) |

TFP410 |

| 25 | DVI_DATA22 | DSS_D22(mode=0) | LCD pixel data bit |

DSS_D4 (mode=3) |

TFP410 |

| 26 | DVI_DATA23 | DSS_D23(mode=0) | LCD pixel data bit |

DSS_D5(mode=3) |

TFP410 |

| 27 | I2C3_SCL | I2C3_SCL(mode=0) | I2C3 Clock | GPIO_184(mode=4) SAFE_MODE(mode=7) |

TXS0102DCUR |

| 28 | I2C3_SDA | I2C3_SDA(mode=0) | I2C3 Data | GPIO_185(mode=4) SAFE_MODE(mode=7) |

TXS0102DCUR |

| 29 | GPMC_NCS7 | GPT8_PWM_EVT(mode=3) | PWM signal | GPMC_NCS7(mode=0) GPMC_IO_DIR(mode=1) MCBSP4_FSX(mode=2) GPIO_58(mode=4) SAFE_MODE(mode=7) |

- |

| 30 | MCSPI1_CS3 | MCSPI1_CS3(mode=0) | SPI1 Chip select 3 | HSUSB2_TLL_DATA2(mode=2) HSUSB2_DATA2(mode=3) GPIO_177(mode=4) MM2_TXDAT(mode=5) SAFE_MODE(mode=7) |

LBEP5CLWMC |

TFP410: converts DVI signal to HDMI

TXS0102DCUR: Increse I2c3 voltage to 5V to read EDID information

LBEP5CLWMC: Wifi and Bluetooth chip on IGEP0020-RG

JA42 connector

JA42 is used for DVI (Digital Video Interface) control part, TouchScreen control and SPI1.

The current available on the DC_5V rail is limited to the available current that remains from the DC supply that is connected to the DC power jack on the board. Keep in mind that some of that power is needed by the USB Host power rail and if more power is needed for the expansion board, the main DC power supply current capability may need to be increased. All signals are 1.8V except the DVI_PUP which is a 3.3V signal. The 1.8V rail is for level translation only and should not be used to power circuitry on the board. The 3.3V rail also has limited capacity on the power as well. It is suggested that the 5V rail be used to generate the required voltages for an adapter card.

- Note that only IGEPv2 RG version has all 22 pads available. Other boards have only first 20 pads available.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | VIO 1V8 | - | Power 1v8 | - | - |

| 2 | SYS_BOOT5 | GPIO_7(mode=4) | Omap boot config |

SYS_BOOT5(mode=0) |

- |

| 3 | DC_5V | - | Power 5v | - | - |

| 4 | GND | - | GND | - | - |

| 5 | SYS_BOOT0 | GPIO_2(mode=4) | Omap boot config | SYS_BOOT0(mode=0) DSS_DATA18(mode=3) SAFE_MODE(mode=7) |

- |

| 6 | SYS_BOOT1 | GPIO_3(mode=4) | Omap boot config | SYS_BOOT1(mode=0) DSS_DATA19(mode=3) SAFE_MODE(mode=7) |

- |

| 7 | DVI_VSYNC | DSS_VSYNC(mode=0) | LCD vertical sync (Expansion) | GPIO_68(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 8 | DVI_HSYNC | DSS_HSYNC(mode=0) | LCD Horitzontal sync (Expansion) | GPIO_67 (mode=4) HW_DBG13(mode=5) SAFE_MODE(mode=7) |

TFP410 |

| 9 | DVI_ACBIAS | DSS_ACBIAS(mode=0) | LCD Control (Expansion) | GPIO_69(mode=4) SAFE_MODE(mode=7) |

TFP410 |

| 10 | DVI_PUP | GPIO_170(mode=4) | Control signal for DVI controller (Expansion) |

HDQ_SIO(mode=0) |

TFP410 |

| 11 | DVI_PCLK | DSS_PCLK(mode=0) | LCD clock (Expansion) | GPIO_66(mode=4) HW_DBG12(mode=5) SAFE_MODE(mode=7) |

TFP410 |

| 12 | TS_nPEN_IRQ | GPIO_175(mode=4) | Touchscreen control (Expansion) | McSPI1_CS1(mode=0) MMC3_CMD(mode=3) SAFE_MODE(mode=7) |

- |

| 13 | LCD_QVGA/nVGA | GPIO_154(mode=4) | Touchscreen control (Expansion) | McBSP4_DX(mode=0) HSUSB3_TLL_DATA2(mode=5) MM3_TXDAT(mode=6) SAFE_MODE(mode=7) |

- |

| 14 | LCD_ENVDD | GPIO_153(mode=4) | Touchscreen control (Expansion) | McBSP4_DR(mode=0) HSUSB3_TLL_DATA0(mode=5) MM3_RXRCV(mode=6) SAFE_MODE(mode=7) |

- |

| 15 | LCD_RESB | GPIO_155(mode=4) | Touchscreen control (Expansion) | McBSP4_FSX(mode=0) HSUSB3_TLL_DATA3(mode=5) MM3_TXEN_N(mode=6) SAFE_MODE(mode=7) |

- |

| 16 | LCD_INI | GPIO_152(mode=4) | Touchscreen control (Expansion) | McBSP4_CLKX(mode=0) HSUSB3_TLL_DATA1(mode=5) MM3_TXSE0(mode=6) SAFE_MODE(mode=7) |

- |

| 17 | MCSPI1_CLK | McSPI1_CLK(mode=0) | Touchscreen control (Expansion) |

MMC2_DAT4(mode=1) |

- |

| 18 | MCSPI1_SIMO | McSPI1_SIMO(mode=0) | Touchscreen control (Expansion) |

MMC2_DAT5(mode=1) |

- |

| 19 | MCSPI1_CS0 | McSPI1_CS0(mode=0) | Touchscreen control (Expansion) |

MMC2_DAT7(mode=1) |

- |

| 20 | MCSPI1_SOMI | McSPI1_SOMI(mode=0) | Touchscreen control (Expansion) |

MMC2_DAT6(mode=1) |

- |

| 21 | GPMC_NCS7 | GPT8_PWM_EVT(mode=3) | PWM signal | GPMC_NCS7(mode=0) GPMC_IO_DIR(mode=1) MCBSP4_FSX(mode=2) GPIO_58(mode=4) SAFE_MODE(mode=7) |

- |

| 22 | MCSPI1_CS3 | MCSPI1_CS3(mode=0) | SPI1 Chip select 3 | HSUSB2_TLL_DATA2(mode=2) HSUSB2_DATA2(mode=3) GPIO_177(mode=4) MM2_TXDAT(mode=5) SAFE_MODE(mode=7) |

LBEP5CLWMC |

TFP410: converts DVI signal to HDMI

LBEP5CLWMC: Wifi and Bluetooth chip on IGEP0020-RG

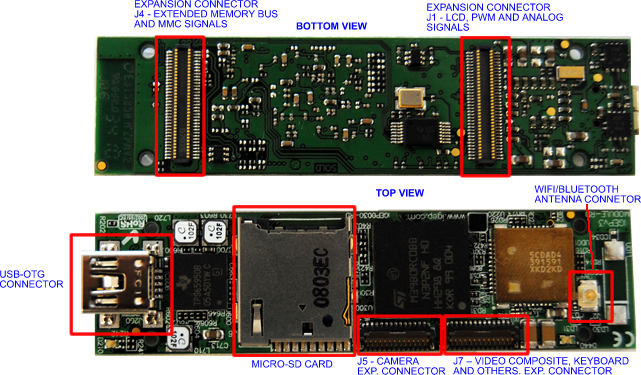

IGEP0030 revisions

| Revision | Name | Comments |

| IGEP0030-RE6 | IGEP COM MODULE | These boards are marked with 6 hand-made number on silkscreen (before 2012 year) or Datamatrix code label "IGEP0030-RE6" (2012 and later). |

| IGEP0030-RE62 | IGEP COM MODULE | These boards are marked with Datamatrix code label "IGEP0030-RE6x". They were sold since 2011.

These boards are like IGEP0030-RE6 plus manufacturing improvements and solve hardware bugs. |

| IGEP0030-RE7 | IGEP COM MODULE | These boards are marked with 7 hand-made number on silkscreen (before 2012 year) or Datamatrix code label "IGEP0030-RE7" (2012 and later). |

| IGEP0030-RE71 / IGEP0030-RE72 | IGEP COM MODULE | These boards are marked with Datamatrix code label "IGEP0030-RE7x". They were sold since 2012.

These boards are like IGEP0030-RE7 plus manufacturing improvements and solve hardware bugs. |

IGEP0030 expansion connectors

|

NOTE: By default, J7 connector is not mounted

J5 connector

OMAP3 processor family has Camera Image Signal Processing (ISP) interface. ISP interface could to be connecting to CCD and CMOS image sensors.

Detailed features of ISP are:

- CCD and CMOS Imager Interface

- Memory Data Input

- BT.601/BT.656 Digital YCbCr 4:2:2 (8-/10-Bit) Interface

- Glueless Interface to Common Video Decoders

- Resize Images From 1/4x to 4x

- Separate Horizontal/Vertical Control

The signals of connector J5 are connected directly to the processor.

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | GPIO94_CAM_HS | CAM_HS(mode=0) | LCD Horitzontal sync | GPIO_94(mode=4) HW_DBG0(mode=5) SAFE_MODE(mode=7) |

- |

| 2 | GPIO95_CAM_VS | GPIO_95(mode=4 | - | xGPIO_95(mode=4) HW_DBG1(mode=5) SAFE_MODE(mode=7) |

- |

| 3 | GPIO96_CAM_XCLKA | CAM_XCLKA(mode=0) | Camera interface | GPIO_96(mode=4) SAFE_MODE(mode=7) |

- |

| 4 | GPIO97_CAM_PCLK | CAM_PCLK(mode=0) | Camera interface | GPIO_97(mode=4) HW_DBG2(mode=5) SAFE_MODE(mode=7) |

- |

| 5 | GPIO98_CAM_FLD | GPIO_98(mode=4) | - | CAM_FLD(mode=0) CAM_GLOBAL_RESET(mode=2) HW_DBG3(mode=5) SAFE_MODE(mode=7) |

- |

| 6 | GPIO99_CAM_D0 | CAM_D0(mode=0) | Camera interface | GPIO_99(mode=4) SAFE_MODE(mode=7) |

- |

| 7 | GPIO100_CAM_D1 | CAM_D1(mode=0) | Camera interface | GPIO_100(mode=4) SAFE_MODE(mode=7) |

- |

| 8 | GPIO101_CAM_D2 | CAM_D2(mode=0) | Camera interface | GPIO_101(mode=4) HW_DBG4(mode=5) SAFE_MODE(mode=7) |

- |

| 9 | GPIO102_CAM_D3 | CAM_D3(mode=0) | Camera interface | GPIO_102(mode=4) HW_DBG5(mode=5) SAFE_MODE(mode=7) |

- |

| 10 | GPIO103_CAM_D4 | CAM_D4(mode=0) | Camera interface | GPIO_103(mode=4) HW_DBG6(mode=5) SAFE_MODE(mode=7) |

- |

| 11 | GPIO104_CAM_D5 | CAM_D5(mode=0) | Camera interface | GPIO_104(mode=4) HW_DBG7(mode=5) SAFE_MODE(mode=7) |

- |

| 12 | GPIO105_CAM_D6 | CAM_D6(mode=0) | Camera Interface | GPIO_105(mode=4) SAFE_MODE(mode=7) |

- |

| 13 | GPIO106_CAM_D7 | CAM_D7(mode=0) | Camera interface | GPIO_106(mode=4) SAFE_MODE(mode=7) |

- |

| 14 | GPIO107_CAM_D8 | CAM_D8(mode=0) | Camera interface | GPIO_107(mode=4) SAFE_MODE(mode=7) |

- |

| 15 | GPIO108_CAM_D9 | CAM_D9(mode=0) | Camera interface | GPIO_108(mode=4) SAFE_MODE(mode=7) |

- |

| 16 | GPIO109_CAM_D10 | CAM_D10(mode=0) | Camera interface | GPIO_109(mode=4) HW_DBG8(mode=5) SAFE_MODE(mode=7) |

- |

| 17 | GPIO110_CAM_D11 | CAM_D11(mode=0) | Camera interface | GPIO_110(mode=4) HW_DBG9(mode=5) SAFE_MODE(mode=7) |

- |

| 18 | GPIO111_CAM_XCLKB | CAM_XCLKB(mode=0) | Camera interface | GPIO_111(mode=4) SAFE_MODE(mode=7) |

- |

| 19 | GPIO167_CAM_WEN | GPIO_167(mode=4) | - | CAM_WEN(mode=0) CAM_SHUTTER(mode=2) HW_DBG10(mode=5) SAFE_MODE(mode=7) |

- |

| 20 | GPIO126_CAM_STROBE | CAM_STROBE(mode=4) | Camera interface | GPIO_126(mode=4) HW_DBG11(mode=5) SAFE_MODE(mode=7) |

- |

| 21 | VIO_1V8 | - | Power 1V8 | - | - |

| 22 | PMIC_SYSEN | - | Control Slave power ICs | - | TPS65950: CONTROL |

| 23 | GND | - | GND | - | - |

| 24 | VBAT | - | Board supply: 3V5-4V2 | - | - |

| 25 | GPIO63_CAM_IRQ | GPMC_WAIT1(mode=0) | - | GPIO_63(mode=4) SAFE_MODE(mode=7) |

- |

| 26 | GPIO184_I2C3_SCL | I2C3_SCL(mode=0) | I2C Clock | GPIO_184(mode=4) SAFE_MODE(mode=7) |

J1 connector |

| 27 | GPIO185_I2C3_SDA | I2C3_SDA(mode=0) | I2C Data | GPIO_185(mode=4) SAFE_MODE(mode=7) |

J1 connector |

Expansion connectors interfaces

The IGEP MODULE has 2 connectors of 70-pin with up to 140 signals at 1V8 CMOS to suport lots of features provided by OMAP3 processor that can be used in your custom baseboard.

J1 connector

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | nRESET | - | Read Reset Omap | - | - |

| 2 | DSS_D1 | DSS_DATA1(mode=0) | LCD pixel data bit | UART1_CTS(mode=2) DSSVENC656_DATA1(mode=3) GPIO_71(mode=4) SAFE_MODE(mode=7) |

- |

| 3 | DSS_D0 | DSS_DATA0(mode=0) | LCD pixel data bit |

UART1_RTS(mode=2) |

- |

| 4 | DSS_D3 | DSS_DATA3(mode=0) | LCD pixel data bit | DSSVENC656_DATA3(mode=3) GPIO_73(mode=4) SAFE_MODE(mode=7) |

- |

| 5 | DSS_D5 | DSS_DATA5(mode=0) | LCD pixel data bit |

UART3_TX(mode=2) |

- |

| 6 | DSS_D2 | DSS_DATA2(mode=0) | LCD pixel data bit | DSSVENC656_DATA2(mode=3) GPIO_72(mode=4) SAFE_MODE(mode=7) |

- |

| 7 | DSS_D4 | DSS_DATA4(mode=0) | LCD pixel data bit |

UART3_RX(mode=2) |

- |

| 8 | GPIO10_SYSCLK1 | SYS_CLKOUT1(mode=0) | Configurable output clock1 | GPIO_10(mode=4) SAFE_MODE(mode=7) |

- |

| 9 | GPIO00_SYSnIRQ0 | SYS_NIRQ(mode=0) | External interrupt | GPIO_0(mode=4) SAFE_MODE(mode=7) |

TPS65950:CONTROL |

| 10 | GPIO185_I2C3_SDA | I2C3_SDA(mode=0) | I2C3 Data | GPIO_185(mode=4) SAFE_MODE(mode=7) |

J5 connector |

| 11 | DSS_D10 | DSS_DATA10(mode=0) | LCD pixel data bit | GPIO_80(mode=4) SAFE_MODE(mode=7) |

- |

| 12 | DSS_D11 | DSS_DATA11(mode=0) | LCD pixel data bit | GPIO_81(mode=4) SAFE_MODE(mode=7) |

- |

| 13 | GPIO184_I2C3_SCL | I2C3_SCL(mode=0) | I2C3 Clock | GPIO_184(mode=0) SAFE_MODE(mode=7) |

J5 connector |

| 14 | GPIO186_SYSCLK2 | GPIO_186(mode=4) | - | SYS_CLKOUT2(mode=0) SAFE_MODE(mode=7) |

- |

| 15 | DSS_D22 | DSS_DATA22(mode=0) | LCD pixel data bit |

MCSPI3_CS1(mode=2) |

- |

| 16 | GPIO147_GPT8_PWM | SAFE_MODE(mode=7) | - | UART2_RX(mode=0) MCBSP3_FSX(mode=1) gpt8_PWM_EVT(mode=2) GPIO_147(mode=4) |

- |

| 17 | DSS_D13 | DSS_DATA13(mode=0) | LCD pixel data bit | GPIO_83(mode=4) SAFE_MODE(mode=7) |

- |

| 18 | GPIO144_GPT9_PWM | UART2_CTS(mode=0) | UART2 Clear to send | MCBSP3_DX(mode=1) GPT9_PWM_EVT(mode=2) GPIO_144(mode=4) SAFE_MODE(mode=7) |

- |

| 19 | DSS_D14 | DSS_DATA14(mode=0) | LCD pixel data bit | GPIO_84(mode=4) SAFE_MODE(mode=7) |

- |

| 20 | DSS_D15 | DSS_DATA15(mode=0) | LCD pixel data bit | GPIO_85(mode=4) SAFE_MODE(mode=7) |

- |

| 21 | GPIO146_GPT11_PWM | SAFE_MODE(mode=7) | - |

UART2_TX(mode=0) |

- |

| 22 | GPIO163_IR_CTS3 | UART3_CTS(mode=0) | UART3 Clear to send | GPIO_163(mode=4) SAFE_MODE(mode=7) |

- |

| 23 | DSS_D21 | DSS_DATA21(mode=0) | LCD pixel data bit | MCSPI3_CS0(mode=2) DSS_DATA3(mode=3) GPIO_91(mode=4) SAFE_MODE(mode=7) |

- |

| 24 | DSS_D17 | DSS_DATA17(mode=0) | LCD pixel data bit | GPIO_87(mode=4) SAFE_MODE(mode=7) |

- |

| 25 | DSS_D18 | DSS_DATA18(mode=0) | LCD pixel data bit | MCSPI3_CLK(mode=2) DSS_DATA0(mode=3) GPIO_88(mode=4) SAFE_MODE(mode=7) |

- |

| 26 | GPIO166_IR_TXD3 | UART3_TX(mode=0) | UART· transfer data | GPIO_166(mode=4) SAFE_MODE(mode=7) |

- |

| 27 | DSS_D19 | DSS_DATA19(mode=0) | LCD pixel data bit | MCSPI3_SIMO(mode=2) DSS_DATA1(mode=3) GPIO_89(mode=4) SAFE_MODE(mode=7) |

- |

| 28 | DSS_D9 | DSS_DATA9(mode=0) | LCD pixel data bit | GPIO_79(mode=4) HW_DBG17(mode=5)SAFE_MODE(mode=7) |

- |

| 29 | DSS_D7 | DSS_DATA7(mode=0) | LCD pixel data bit | UART1_RX(mode=2) DSSVENC656_DATA7(mode=3) GPIO_77(mode=4) HW_DBG15(mode=5) SAFE_MODE(mode=7) |

- |

| 30 | DSS_D8 | DSS_DATA8(mode=0) | LCD pixel data bit | GPIO_78(mode=4) HW_DBG16(mode=5)SAFE_MODE(mode=7) |

- |

| 31 | GPIO165_IR_RXD3 | UART3_RX(mode=0) | UART· Receive data | GPIO_165(mode=4) SAFE_MODE(mode=7) |

- |

| 32 | GPIO66_DSS_PCLK | DSS_PCLK(mode=0) | LCD Clock | GPIO_66(mode=4) HW_DBG12(mode=5) SAFE_MODE(mode=7) |

- |

| 33 | DSS_D6 | DSS_DATA6(mode=0) | LCD pixel data bit | UART1_TX(mode=2) DSSVENC656_DATA6(mode=3) GPIO_76(mode=4) HW_DBG14(mode=5) SAFE_MODE(mode=7) |

- |

| 34 | GPIO68_DSS_VSYNC | DSS_VSYNC(mode=0) | LCD vertical sync | GPIO_68(mode=4) SAFE_MODE(mode=7) |

- |

| 35 | GPIO67_DSS_HSYNC | DSS_SYNC(mode=0) | LCD horitzontal sync | GPIO_67(mode=4) HW_DBG13(mode=5) SAFE_MODE(mode=7) |

- |

| 36 | PMIC_USBOTG_DP | - | - | - | TPS65950:USB;OTG Connector |

| 37 | PMIC_USBOTG_DN | - | - | - | TPS65950:USB;OTG Connector |

| 38 | PMIC_AUXL | - | Auxiliary input left | - | TPS65950:AUX Input |

| 39 | PMIC_MIC_SUB_M | - | MIC | - | TPS65950:ANA_MIC |

| 40 | PMIC_ADCIN4 | - | General purpouse analog input | - | TPS65950:MCPC |

| 41 | PMIC_AUXR | - | Auxiliary input right | - | TPS65950:AUX Input |

| 42 | PMIC_PWM0 | - | PWM0 | - | TPS65950:GPIO |

| 43 | GPIO69_DSS_ACBIAS | DSS_ACBIAS(mode=0) | LCD Control | GPIO_69(mode=4) SAFE_MODE(mode=7) |

- |

| 44 | DSS_D16 | DSS_DATA16(mode=0) | LCD pixel data bit | GPIO_86(mode=4) SAFE_MODE(mode=7) |

- |

| 45 | DSS_D20 | DSS_DATA20(mode=0) | LCD pixel data bit | MCSPI3_SOMI(mode=2) DSS_DATA2(mode=3) GPIO_90(mode=4) SAFE_MODE(mode=7) |

- |

| 46 | PMIC_USBOTG_ID | - | - | - | TPS65950:USB;OTG Connector |

| 47 | GPIO170_HDQ_1WIRE | GPIO_170(mode=4) | - | HDQ_SIO(mode=0) SYS_ALTCLK(mode=1) I2C2_SCCBE(mode=2) I2C3_SCCBE(mode=3) SAFE_MODE(mode=7) |

- |

| 48 | PMIC_ADCIN3 | - | General purpouse analog input | - | TPS65950:MCPC |

| 49 | PMIC_PWM1 | - | PWM1 | - | TPS65950:MCPC |

| 50 | GND | - | GND | - | - |

| 51 | PMIC_ADCIN5 | - | General purpouse analog input | - | TPS65950:MCPC |

| 52 | PMIC_VBACKUP | - | Backup Battery | - | TPS65950:Backup Battery |

| 53 | PMIC_ADCIN6 | - | General purpouse analog input | - | TPS65950:MCPC |

| 54 | PMIC_USBOTG_VBUS | - | - | - | TPS65950:USB |

| 55 | GPIO145:GPT10_PWM | UART2_RTS(mode=0) | UART2 Ready to send |

MCBSP3_DR(mode=1) |

- |

| 56 | GND | - | GND | - | - |

| 57 | PMIC_MIC_MAIN_M | - | MIC | - | TPS65950:ANA_MIC |

| 58 | PMIC_ADCIN2 | - | - | - | TPS65950:ADC |

| 59 | J1_SYSEN | REGEN | Master/Slave control power TPS65950 | - | - |

| 60 | DSS_D12 | DSS_DATA12(mode=0) | LCD pixel data bit | GPIO_82(mode=4) SAFE_MODE(mode=7) |

- |

| 61 | DSS_D23 | DSS_DATA23(mode=0) | LCD pixel data bit | DSS_DATA5(mode=3) GPIO_83(mode=4) SAFE_MODE(mode=7) |

- |

| 62 | GPIO15_MCSPI3_SOMI | GPIO_15(mode=4) | ETK_D1(mode=0) MCSPI3_SOMI(mode=1) HSUSB1_DATA1(mode=3) MM1_TXSE0(mode5) HSUSB3_TLL_DATA1(mode=6) HW_DBG3(mode=7) |

- | |

| 63 | GPIO164_RTS3 | UART3_RTS(mode=0) | UART· Ready to send | GPIO_164(mode=4) SAFE_MODE(mode=7) |

- |

| 64 | PMIC_ADCIN7 | - | General purpouse analog input | - | TPS65950:Headset |

| 65 | PMIC_PWRON | - | Battery control | - | TPS65950:Control |

| 66 | VBAT | - | Board supply: 3V5-4V2 | - | - |

| 67 | VBAT | - | Board supply: 3V5-4V2 | - | - |

| 68 | PMIC_HSOL | - | Headset output left | - | TPS65950:Headset |

| 69 | PMIC_HSOR | - | Headset output right | - | TPS65950:Headset |

| 70 | GND | - | GND | - | - |

J4 connector

| Pad | Pad Name | Initial mode | Main utility | Other available peripherals | Share with |

| 1 | VBAT | - | Board supply: 3V5-4V2 | - | - |

| 2 | VBAT | - | Board supply: 3V5-4V2 | - | - |

| 3 | GND | - | GND | - | - |

| 4 | GPMC_nCS5 | GPMC_nCS5(mode=0) | General purpose memory controller | SYS_NDMAREQ2(mode=1) MCBSP4_DR(mode=2) GPT10_PWM_EVT(mode=3) GPIO_56(mode=4) SAFE_MODE(mode=7) |

- |

| 5 | GPMC_nCS4 | GPMC_nCS4(mode=0) | General purpose memory controller | SYS_NDMAREQ1(mode=1) MCBSP4_CLKX(mode=2) GPT9_PWM_EVT(mode=3) GPIO_55(mode=4) SAFE_MODE(mode=7) |

- |

| 6 | GPMC_nWE | GPMC_nWE | General purpose memory controller | - | - |

| 7 | GPMC_nADV_ALE | GPMC_nADV | General purpose memory controller | - | - |

| 8 | GPMC_nOE | GPMC_nOE | General purpose memory controller | - | - |

| 9 | GPIO65_ETH1_IRQ1 | GPMC_WAIT3(mode=0) | - | SYS_NDMAREQ1(mode=1) UART4_RX(mode=2) GPIO_65(mode=4) SAFE_MODE(mode=7) |

- |

| 10 | GPIO64_ETH0_NRESET | GPIO_64(mode=4) | - | GPMC_WAIT2(mode=0) UART4_TX(mode=2) SAFE_MODE(mode=7) |

- |

| 11 | GPMC_A2 | GPMC_A2(mode=0) | General purpose memory controller | GPIO_35(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 12 | GPMC_A8 | GPMC_A8(mode=0) | General purpose memory controller | GPIO_41(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 13 | GPMC_A5 | GPMC_A5(mode=0) | General purpose memory controller | GPIO_38(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 14 | GPMC_A7 | GPMC_A7(mode=0) | General purpose memory controller | GPIO_40(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 15 | GPMC_D2 | GPMC_D2 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 16 | GPMC_D10 | GPMC_D10(mode=0) | General purpose memory controller | GPIO_46(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 17 | GPMC_D3 | GPMC_D3 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 18 | GPMC_D11 | GPMC_D11(mode=0) | General purpose memory controller | GPIO_47(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 19 | GPMC_D4 | GPMC_D4 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 20 | GPMC_D12 | GPMC_D12(mode=0) | General purpose memory controller | GPIO_48(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 21 | GPMC_D5 | GPMC_D5 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 22 | GPMC_D15 | GPMC_D15(mode=0) | General purpose memory controller | GPIO_51(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 23 | GPIO13_MMC3_CMD | GPIO_13(mode=4) | - | ETK_CTL(mode=0) MMC3_CMD(mode=2) HSUSB1_CLK(mode=3) HSUSB1_TLL_CLK(mode=6) HW_DBG1(mode=7) |

- |

| 24 | GPIO148_TXD1 | UART1_TX(mode=0) | Transmited serial UART | GPIO_148(mode=4) SAFE_MODE(mode=7) |

- |

| 25 | GPIO176_SPI1_CS2 | GPIO_176(mode=4) | - | MCSPI1_CS2(mode=0) MMC3_CLK(mode=3) SAFE_MODE(mode=7) |

- |

| 26 | GPIO18_MMC3_D0 | GPIO_18(mode=4) | - | ETK_D4(mode=0) MCBSP5_DR(mode=1) MMC3_DAT0(mode=2) HSUSB1_DATA4(mode=3) HSUSB1_TLLDATA4(mode=6) HW_DBG6(mode=7) |

- |

| 27 | GPIO174_SPI1_CS2 | McSPI1_CS0(mode=0) | Chip select 0 | MMC2_DAT7(mode=1) GPIO_174(mode=4) SAFE_MODE(mode=7) |

- |

| 28 | GPIO53_GPMC_nCS2 | GPIO_53(mode=4) | - | GPMC_NCS2(mode=0) SAFE_MODE(mode=7) |

- |

| 29 | GPIO14_MMC3_D4 | GPIO_14(mode=4) | - | ETK_D0(mode=0) MCSPI3_SIMO(mode=1) MMC3_DAT4(mode=2) HSUSB1_DATA0(mode=3) MM1_RXCV(mode=5) HSUSB1_TLL_DATA0(mode=6) HW_DBG2(mode=7) |

- |

| 30 | GPIO21_MMC3_D7 | GPIO_21(mode=4) | - | ETK_D7(mode=0) MCSPI3_CS1(mode=1) MMC3_DAT7(mode=2) HSUSB1_DATA3(mode=3) MM1_TXEN_N(mode=5) HSUSB1_TLL_DATA3(mode=6) HW_DBG9(mode=7) |

- |

| 31 | GPIO17_MMC3_D3 | GPIO_17(mode=4) | - | ETK_D3(mode=0) MCSPI3_CLK(mode=1) MMC3_DAT3(mode=2) HSUSB1_DATA7(mode=3) HSUSB1_TLL_DATA7(mode=6) HW_DBG5(mode=7) |

- |

| 32 | HUSBH_VBUS | - | USB2 | - | USB3326 |

| 33 | GND | - | GND | - | - |

| 34 | HSUSB_DP | - | USB2 | - | USB3326 |

| 35 | HSUSB_DM | - | USB2 | - | USB3326 |

| 36 | GPIO19_MMC3_D1 | GPIO_19(mode=4) | - | ETK_D5(mode=0) MCSPI5_FSX(mode=1) MMC3_DAT1(mode=2) HSUSB1_DATA5(mode=3) HSUSB1_TLL_DATA5(mode=6) HW_DBG7(mode=7) |

- |

| 37 | GPIO22_MMC3_D6 | SYS_DRM_MSECURE(mode=1) | - | ETK_D8(mode=0) MMC3_DAT6(mode=2) HSUSB1_DIR(mode=3) GPIO_22(mode=4) HSUSB1_TLL_DIR(mode=6) HW_DBG10(mode=7) |

- |

| 38 | GPIO23_MMC3_D5 | GPIO_23(mode=4) | - | ETK_D9(mode=0) SYS_SECURE_INDICATOR(mode=1) MMC3_DAT5(mode=2) HSUSB1_NXT(mode=3) HSUSB1_TLL_NXT(mode=6) HW_DBG11(mode=7) |

- |

| 39 | GPIO20_MMC3_D2 | GPIO_20(mode=4) | - | ETK_D6(mode=0) MCBSP5_DX(mode=1) MMC3_DAT2(mode=2) HSUSB1_DATA6(mode=3) HSUSB1_TLL_DATA6(mode=6) HW_DBG8(mode=7) |

- |

| 40 | GPIO12_MMC3_CLK | GPIO_12(mode=4) | - | ETK_CLK(mode=0) MCBSP5_CLKX(mode=1) MMC3_CLK(mode=2) HSUSB1_STP(mode=3) MM1_RXDP(mode=5) HSUSB1_TLL_STP(mode=6) HW_DBG0(mode=7) |

- |

| 41 | GPIO114_SPI1_NIRQ | GPIO_114(mode=4) | - | SAFE_MODE(mode=7) | - |

| 42 | GPIO175_SPI1_CS1 | GPIO_175(mode=4) | - | MCSPI1_CS1(mode=0) MMC3_CMD(mode=3) SAFE_MODE(mode=7) |

- |

| 43 | GPIO171_SPI1_CLK | McSPI1_CLK(mode=0) | Clock |

MMC2_DAT4(mode=1) |

- |

| 44 | GPIO172_SPI1_SIMO | McSPI1_SIMO(mode=0) | Slave input master output |

MMC2_DAT5(mode=1) GPIO_172(mode=4) SAFE_MODE(mode=7) |

- |

| 45 | GPIO173_SPI1_SOMI | McSPI1_SOMI(mode=0) | Slave output master input |

MMC2_DAT6(mode=1) GPIO_173(mode=4) SAFE_MODE(mode=7) |

- |

| 46 | GPIO149_MMC3_CD | UART1_RTS(mode=0) | Uart ready to send | GPIO_149(mode=4) SAFE_MODE(mode=7) |

- |

| 47 | GPIO150_MMC3_WP | UART1_CTS(mode=0) | Uart clear to send | GPIO_150(mode=4) HSUSB3_TLL_CLK(mode=6) SAFE_MODE(mode=7) |

- |

| 48 | GPIO151_RXD1 | UART1_RX(mode=0) | Received serial UART | MCBSP1_CLKR(mode=2) MCSPI4_CLK(mode=3) GPIO_151(mode=4) SAFE_MODE(mode=7) |

- |

| 49 | GPMC_D7 | GPMC_D7 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 50 | GPMC_D14 | GPMC_D14(mode=0) | General purpose memory controller | GPIO_50(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 51 | GPMC_D6 | GPMC_D6 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 52 | GPMC_D13 | GPMC_D13(mode=0) | General purpose memory controller | GPIO_49(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 53 | GPMC_D1 | GPMC_D1 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 54 | GPMC_D8 | GPMC_D8(mode=0) | General purpose memory controller | GPIO_44(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 55 | GPMC_D9 | GPMC_D9(mode=0) | General purpose memory controller | GPIO_45(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 56 | GPMC_D0 | GPMC_D0 | General purpose memory controller | - | Used in the IGEP COM PROTON |

| 57 | GPMC_A6 | GPMC_A6(mode=0) | General purpose memory controller | GPIO_39(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 58 | GPMC_A1 | GPMC_A1(mode=0) | General purpose memory controller | GPIO_34(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 59 | GPMC_A3 | GPMC_A3(mode=0) | General purpose memory controller | GPIO_36(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 60 | GPMC_A10 | GPMC_A10(mode=0) | General purpose memory controller | SYS_NDMAREQ3(mode=1) GPIO_43(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 61 | GPMC_A4 | GPMC_A4(mode=0) | General purpose memory controller | GPIO_37(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 62 | GPMC_A9 | GPMC_A9(mode=0) | General purpose memory controller | SYS_NDMAREQ2(mode=1) GPIO_42(mode=4) SAFE_MODE(mode=7) |

Used in the IGEP COM PROTON |

| 63 | GPMC_nWP | GPMC_nWP(mode=0) | General purpose memory controller | GPIO_62(mode=4) SAFE_MODE(mode=7) |

- |

| 64 | GPMC_nCS1 | GPMC_nCS1(mode=0) | General purpose memory controller | GPIO_52(mode=4) SAFE_MODE(mode=7) |

- |

| 65 | GPMC_nBE0_CLE | GPMC_nBE0(mode=0) | General purpose memory controller | GPIO_60(mode=4) SAFE_MODE(mode=7) |

- |

| 66 | GPMC_nCS0 | GPMC_nCS0 | General purpose memory controller | - | - |

| 67 | GPMC_nCS6 | GPMC_nCS6(mode=0) | General purpose memory controller | MCBSP4_DX(mode=2) GPT11_PWM_EVT(mode=3) GPIO_57(mode=4) SAFE_MODE(mode=7) |

- |

| 68 | GPMC_WAIT0 | GPMC_WAIT0(mode=0) | General purpose memory controller | - | - |

| 69 | GPMC_nBE1 | GPMC_nBE1(mode=0) | General purpose memory controller | GPIO_61(mode=4) SAFE_MODE(mode=7) |

- |

| 70 | GPMC_CLK | GPMC_CLK(mode=0) | General purpose memory controller | GPIO_59(mode=4) SAFE_MODE(mode=7) |

- |

USB3326: Miniature Hi-Speed USB Transceiver

IGEP0032 revisions

| Revision | Name | Comments |

| IGEP0032-RA1 | IGEP COM PROTON |

IGEP Expansion Boards

IGEP0022 revisions

| Revision | Name | Comments |

| IGEP0022-RA | IGEPv2 EXPANSION | These boards are marked on silkscreen. They were sold on 2010-3Q |

| IGEP0022-RB | IGEPv2 EXPANSION | These boards are marked on silkscreen. They were sold on 2011-1Q |

| IGEP0022-RC | IGEPv2 EXPANSION | These boards are marked with Datamatrix code label. They were sold on 2011-3Q |

BASE0010 revisions

| Revision | Name | Comments |

| BASE0010-RA1 | IGEPv3-BASE RA | They were sold on 2011-1Q |

| BASE0010-RB3 | IGEP BERLIN | |

| BASE0010-RB4 | IGEP PARIS |

ILMS0015 revisions

| Revision | Name | Comments |

| ILMS0015-RA2 | IGEP NEW YORK |

IGEP Radar

RADR0000 revisions

| Revision | Name | Comments |

| RADR0000 / DNRA.0010.B2 & IGEP0020-RB1 | RADR0000 or IGEP Radar Kit v1 | It is the assembly of two boards. The radar sensor board manufactured in 2010 and the processor Board in period 2009 to 2010 without WiFi |

RADR0010 revisions

| Revision | Name | Comments |

| RADR0010-RA1 | IGEP RADAR SENSOR ORION or IGEP Radar v2 | It is a single radar board manufactured in 2011. |