User:Pau pajuelo

From IGEP - ISEE Wiki

Contents

TODO:

Categorize new tutorials

How to manage the kernel modules on Linux

How do I edit my kernel command line

Basic Software instructions

Make a flash backup to a microSD and restore

Change your static IP to IGEP Firmware

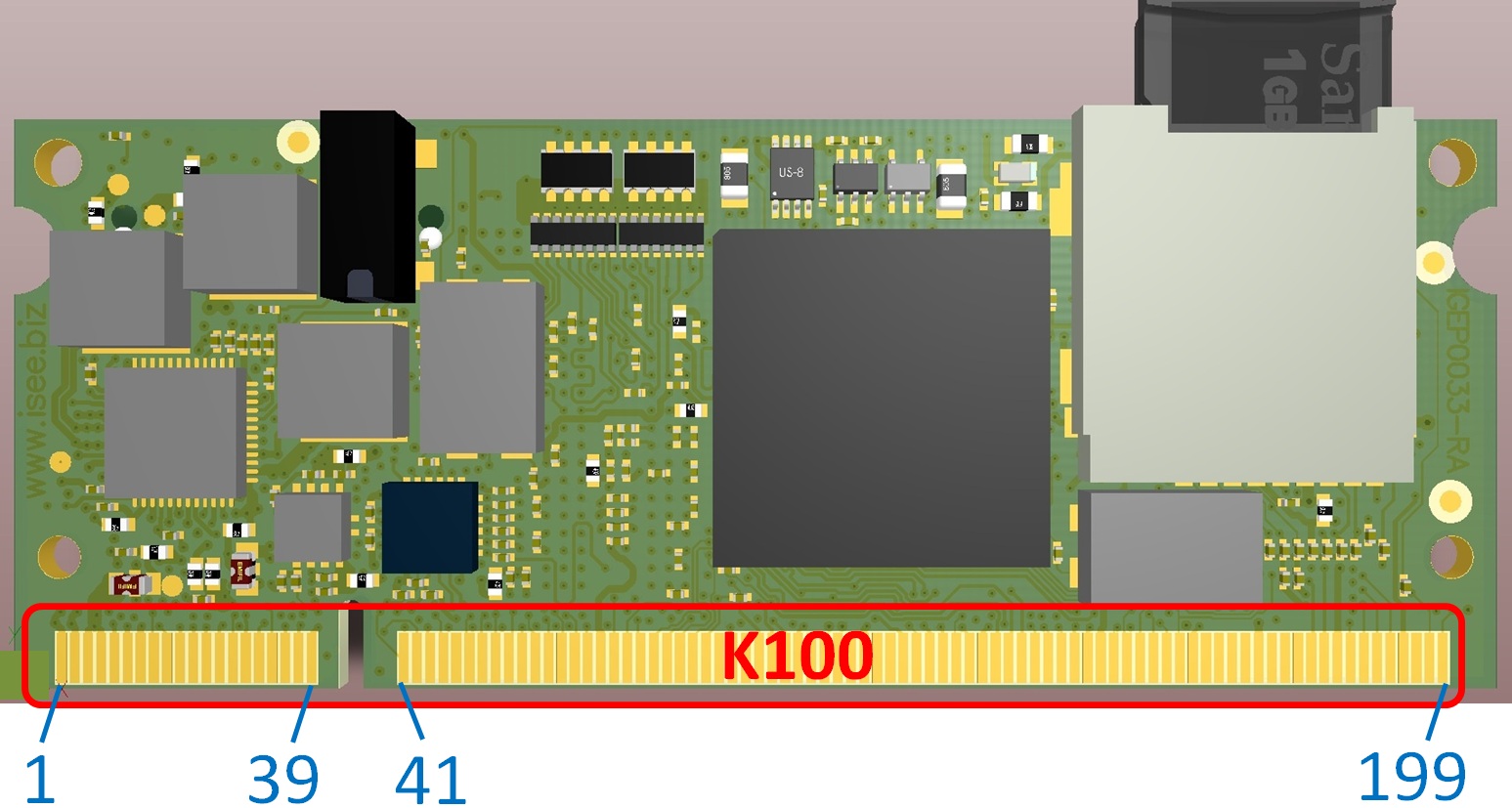

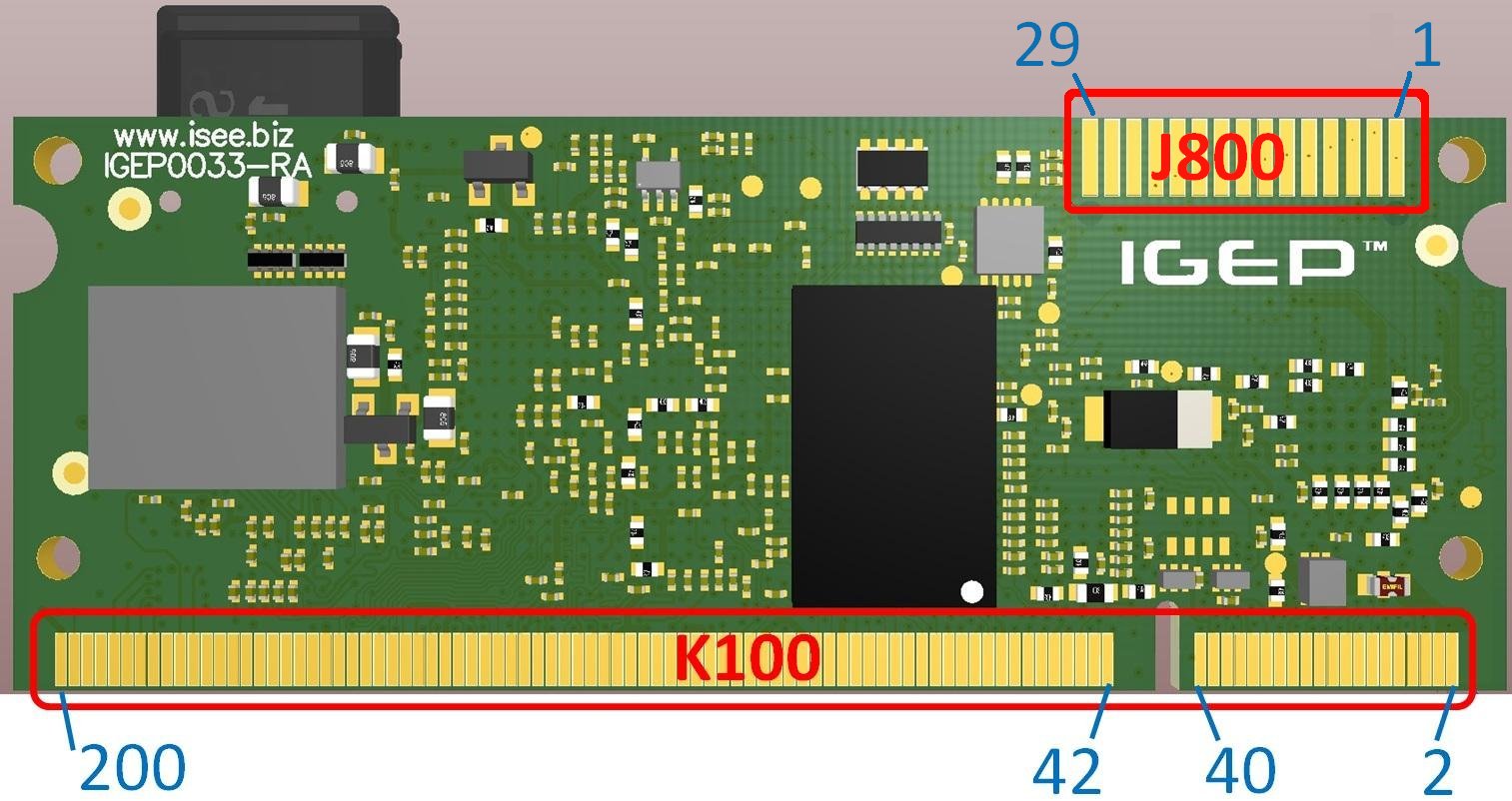

IGEP0033 CONNECTOR SUMMARY TABLE

|

|

K100 SODIMM 200 connector

Short introduction

| Pad | Initial Mode | Main utility | BASE0033 utility | Other available peripherals | Share with |

| 5V INPUT POWER | |||||

| 1 2 3 4 |

- | Input 5V | Input 5V | - | - |

| 3V3 OUTPUT POWER | |||||

| 5 6 7 |

- | Output 5V | Output 5V | - | - |

| BOOT MODE | |||||

| 8 | DSS_D2 | DSS_DATA2(mode=0) | LCD pixel data bit | - | - |

| 3V3 OUTPUT POWER | |||||

| 7 | DSS_D4 | DSS_DATA4(mode=0) | LCD pixel data bit |

UART3_RX(mode=2) |

- |

| CONTROL SIGNALS | |||||

| 8 | GPIO10_SYSCLK1 | SYS_CLKOUT1(mode=0) | Configurable output clock1 | GPIO_10(mode=4) SAFE_MODE(mode=7) |

- |

| 9 | GPIO00_SYSnIRQ0 | SYS_NIRQ(mode=0) | External interrupt | GPIO_0(mode=4) SAFE_MODE(mode=7) |

TPS65950:CONTROL |

| 10 | GPIO185_I2C3_SDA | I2C3_SDA(mode=0) | I2C3 Data | GPIO_185(mode=4) SAFE_MODE(mode=7) |

J5 connector |

| 11 | DSS_D10 | DSS_DATA10(mode=0) | LCD pixel data bit | GPIO_80(mode=4) SAFE_MODE(mode=7) |

- |

| 12 | DSS_D11 | DSS_DATA11(mode=0) | LCD pixel data bit | GPIO_81(mode=4) SAFE_MODE(mode=7) |

- |

| 13 | GPIO184_I2C3_SCL | I2C3_SCL(mode=0) | I2C3 Clock | GPIO_184(mode=0) SAFE_MODE(mode=7) |

J5 connector |

| 14 | GPIO186_SYSCLK2 | GPIO_186(mode=4) | - | SYS_CLKOUT2(mode=0) SAFE_MODE(mode=7) |

- |

| 15 | DSS_D22 | DSS_DATA22(mode=0) | LCD pixel data bit |

MCSPI3_CS1(mode=2) |

- |

| 16 | GPIO147_GPT8_PWM | SAFE_MODE(mode=7) | - | UART2_RX(mode=0) MCBSP3_FSX(mode=1) gpt8_PWM_EVT(mode=2) GPIO_147(mode=4) |

- |

| 17 | DSS_D13 | DSS_DATA13(mode=0) | LCD pixel data bit | GPIO_83(mode=4) SAFE_MODE(mode=7) |

- |

| 18 | GPIO144_GPT9_PWM | UART2_CTS(mode=0) | UART2 Clear to send | MCBSP3_DX(mode=1) GPT9_PWM_EVT(mode=2) GPIO_144(mode=4) SAFE_MODE(mode=7) |

- |

| 19 | DSS_D14 | DSS_DATA14(mode=0) | LCD pixel data bit | GPIO_84(mode=4) SAFE_MODE(mode=7) |

- |

| 20 | DSS_D15 | DSS_DATA15(mode=0) | LCD pixel data bit | GPIO_85(mode=4) SAFE_MODE(mode=7) |

- |

| 21 | GPIO146_GPT11_PWM | SAFE_MODE(mode=7) | - |

UART2_TX(mode=0) |

- |

| 22 | GPIO163_IR_CTS3 | UART3_CTS(mode=0) | UART3 Clear to send | GPIO_163(mode=4) SAFE_MODE(mode=7) |

- |

| 23 | DSS_D21 | DSS_DATA21(mode=0) | LCD pixel data bit | MCSPI3_CS0(mode=2) DSS_DATA3(mode=3) GPIO_91(mode=4) SAFE_MODE(mode=7) |

- |

| 24 | DSS_D17 | DSS_DATA17(mode=0) | LCD pixel data bit | GPIO_87(mode=4) SAFE_MODE(mode=7) |

- |

| 25 | DSS_D18 | DSS_DATA18(mode=0) | LCD pixel data bit | MCSPI3_CLK(mode=2) DSS_DATA0(mode=3) GPIO_88(mode=4) SAFE_MODE(mode=7) |

- |

| 26 | GPIO166_IR_TXD3 | UART3_TX(mode=0) | UART· transfer data | GPIO_166(mode=4) SAFE_MODE(mode=7) |

- |

| 27 | DSS_D19 | DSS_DATA19(mode=0) | LCD pixel data bit | MCSPI3_SIMO(mode=2) DSS_DATA1(mode=3) GPIO_89(mode=4) SAFE_MODE(mode=7) |

- |

| 28 | DSS_D9 | DSS_DATA9(mode=0) | LCD pixel data bit | GPIO_79(mode=4) HW_DBG17(mode=5)SAFE_MODE(mode=7) |

- |

| 29 | DSS_D7 | DSS_DATA7(mode=0) | LCD pixel data bit | UART1_RX(mode=2) DSSVENC656_DATA7(mode=3) GPIO_77(mode=4) HW_DBG15(mode=5) SAFE_MODE(mode=7) |

- |

| 30 | DSS_D8 | DSS_DATA8(mode=0) | LCD pixel data bit | GPIO_78(mode=4) HW_DBG16(mode=5)SAFE_MODE(mode=7) |

- |

| 31 | GPIO165_IR_RXD3 | UART3_RX(mode=0) | UART· Receive data | GPIO_165(mode=4) SAFE_MODE(mode=7) |

- |

| 32 | GPIO66_DSS_PCLK | DSS_PCLK(mode=0) | LCD Clock | GPIO_66(mode=4) HW_DBG12(mode=5) SAFE_MODE(mode=7) |

- |

| 33 | DSS_D6 | DSS_DATA6(mode=0) | LCD pixel data bit | UART1_TX(mode=2) DSSVENC656_DATA6(mode=3) GPIO_76(mode=4) HW_DBG14(mode=5) SAFE_MODE(mode=7) |

- |

| 34 | GPIO68_DSS_VSYNC | DSS_VSYNC(mode=0) | LCD vertical sync | GPIO_68(mode=4) SAFE_MODE(mode=7) |

- |

| 35 | GPIO67_DSS_HSYNC | DSS_SYNC(mode=0) | LCD horitzontal sync | GPIO_67(mode=4) HW_DBG13(mode=5) SAFE_MODE(mode=7) |

- |

| 36 | PMIC_USBOTG_DP | - | - | - | TPS65950:USB;OTG Connector |

| 37 | PMIC_USBOTG_DN | - | - | - | TPS65950:USB;OTG Connector |

| 38 | PMIC_AUXL | - | Auxiliary input left | - | TPS65950:AUX Input |

| 39 | PMIC_MIC_SUB_M | - | MIC | - | TPS65950:ANA_MIC |

| 40 | PMIC_ADCIN4 | - | General purpouse analog input | - | TPS65950:MCPC |

| 41 | PMIC_AUXR | - | Auxiliary input right | - | TPS65950:AUX Input |

| 42 | PMIC_PWM0 | - | PWM0 | - | TPS65950:GPIO |

| 43 | GPIO69_DSS_ACBIAS | DSS_ACBIAS(mode=0) | LCD Control | GPIO_69(mode=4) SAFE_MODE(mode=7) |

- |

| 44 | DSS_D16 | DSS_DATA16(mode=0) | LCD pixel data bit | GPIO_86(mode=4) SAFE_MODE(mode=7) |

- |

| 45 | DSS_D20 | DSS_DATA20(mode=0) | LCD pixel data bit | MCSPI3_SOMI(mode=2) DSS_DATA2(mode=3) GPIO_90(mode=4) SAFE_MODE(mode=7) |

- |

| 46 | PMIC_USBOTG_ID | - | - | - | TPS65950:USB;OTG Connector |

| 47 | GPIO170_HDQ_1WIRE | GPIO_170(mode=4) | - | HDQ_SIO(mode=0) SYS_ALTCLK(mode=1) I2C2_SCCBE(mode=2) I2C3_SCCBE(mode=3) SAFE_MODE(mode=7) |

- |

| 48 | PMIC_ADCIN3 | - | General purpouse analog input | - | TPS65950:MCPC |

| 49 | PMIC_PWM1 | - | PWM1 | - | TPS65950:MCPC |

| 50 | GND | - | GND | - | - |

| 51 | PMIC_ADCIN5 | - | General purpouse analog input | - | TPS65950:MCPC |

| 52 | PMIC_VBACKUP | - | Backup Battery | - | TPS65950:Backup Battery |

| 53 | PMIC_ADCIN6 | - | General purpouse analog input | - | TPS65950:MCPC |

| 54 | PMIC_USBOTG_VBUS | - | - | - | TPS65950:USB |

| 55 | GPIO145:GPT10_PWM | UART2_RTS(mode=0) | UART2 Ready to send |

MCBSP3_DR(mode=1) |

- |

| 56 | GND | - | GND | - | - |

| 57 | PMIC_MIC_MAIN_M | - | MIC | - | TPS65950:ANA_MIC |

| 58 | PMIC_ADCIN2 | - | - | - | TPS65950:ADC |

| 59 | J1_SYSEN | REGEN | Master/Slave control power TPS65950 | - | - |

| 60 | DSS_D12 | DSS_DATA12(mode=0) | LCD pixel data bit | GPIO_82(mode=4) SAFE_MODE(mode=7) |

- |

| 61 | DSS_D23 | DSS_DATA23(mode=0) | LCD pixel data bit | DSS_DATA5(mode=3) GPIO_83(mode=4) SAFE_MODE(mode=7) |

- |

| 62 | GPIO15_MCSPI3_SOMI | GPIO_15(mode=4) | ETK_D1(mode=0) MCSPI3_SOMI(mode=1) HSUSB1_DATA1(mode=3) MM1_TXSE0(mode5) HSUSB3_TLL_DATA1(mode=6) HW_DBG3(mode=7) |

- | |

| 63 | GPIO164_RTS3 | UART3_RTS(mode=0) | UART· Ready to send | GPIO_164(mode=4) SAFE_MODE(mode=7) |

- |

| 64 | PMIC_ADCIN7 | - | General purpouse analog input | - | TPS65950:Headset |

| 65 | PMIC_PWRON | - | Battery control | - | TPS65950:Control |

| 66 | VBAT | - | Board supply: 3V5-4V2 | - | - |

| 67 | VBAT | - | Board supply: 3V5-4V2 | - | - |

| 68 | PMIC_HSOL | - | Headset output left | - | TPS65950:Headset |

| 69 | PMIC_HSOR | - | Headset output right | - | TPS65950:Headset |

| 70 | GND | - | GND | - | - |

BASE0033 CONNECTOR SUMMARY TABLE

Configure a static IP using the same private network range

under construction

IGEP Firmware Yocto uses the following Ethernet network configuration (IP addresses)

- eth0 − 192.168.5.1

- eth0:0 − assigned via dhcp.

This Ethernet network configuration is really useful when you work using a Linux operating system like IGEP SDK Virtual Machine. Because you use eth0 device to communicate easily with your board and eth0:0 device to get Internet acces using dhcp protocol.

But some scenarios this network configuration is not useful, for example: if you use a non-Linux operating system, connect to two IP private range interfaces is not simple. This How-to can be useful to

(Make diagram one: IGEP and Linux defualt communication. Diagram 2 IGEP and other SO alternative configuration)

igep.ini parameters

The kernel command line syntax is name=value1. These next parameters are supported in igep.ini since IGEP-X_Loader 2.4.0-2:

[kernel]

| Parameter Name | Description | Default value | Comments |

| kaddress | Kernel copy address | =0x80008000 | Hex memory address |

| rdaddress | Ram Disk location address | =0x81600000 | Hex memory address; disabled by default |

| serial.low | Serial number (low part) | =00000001 | Numeric |

| serial.high | Serial number (high part) | =00000000 | Numeric |

| revision | Revision ID | =0003 | Numeric |

| kImageName | Kernel, binary image name | =zImage | Kernel or binary image name |

| kRdImageName | Kernel RAM Disk Image Name | - | Ram Disk image name |

| MachineID | Machine ID (kernel ID) | ;IGEPv2 =2344 |

;Module =2717 ;Proton =3203 |

| Mode | Boot Mode | ;Linux kernel =kernel |

;Other image (like uboot) [binary image] |

[kparams]

| Parameter Name | Description | Default value | Comments |

| buddy | Enable/disable expansion board support | ;IGEPv2 Expansion Board support =igep0022 |

;Berlin and Paris Expansion Board support =base0010 New York Expansion =ilms0015 |

| console | Setup the kernel console parameters | =ttyO2,115200n8 | - |

| earlyprintk | Enable early printk | - | - |

| mem | Setup the Board Memory Configuration | =430M | - |

| boot_delay | Setup the boot delay | =0 | - |

| mpurate | Setup ARM Processor Speed | - | - |

| loglevel | Setup the loglevel | - | - |

| debug | Enable kernel debug output | - | - |

| fixrtc | Fix RTC variable | - | - |

| nocompcache | Configure nocompcache variable | =1 | - |

| omapfb.mode | Configure frame bugger configuration | =dvi:hd720-16@50 | ;Other configuration =dvi:1280x720MR-16@60 |

| vram | Configure Video RAM assigned to every frame buffer | - | - |

| omapfb.vram | Configure Video RAM assigned to every frame buffer | - | - |

| omapfb.debug | Configure frame buffer debug output | - | - |

| omapdss.debug | Configure DSS Video debug output | - | - |

| smsc911x.mac0 | Configure Board Ethernet Mac Address | =0xb2,0xb0,0x14,0xb5,0xcd,0xde | For IGEP BERLIN |

| smsc911x.mac1 | Configure Board Ethernet Mac Address | =0xb2,0xb0,0x14,0xb5,0xcd,0xdf | For IGEP BERLIN (only with IGEP PROTON) |

| smsc911x.mac | Configure Board Ethernet Mac Address | =0xb2,0xb0,0x14,0xb5,0xcd,0xde | For IGEPv2, IGEP PROTON, IGEP PARIS and IGEP BERLIN |

| ubi.mtd | Fot UBI FS boot | - | - |

| root | Configure root directory for MMC, NFS or UBI | ;For mmc memory =/dev/mmcblk0p2 rw rootwait |

;For flash memory =/dev/mtdblock2 |

| nfsroot | For NFS boot | - | - |

| rootfstype | For UBI FS boot | - | - |

| ip | For NFS boot | - | - |

| init | Assign init program | - | - |

| musb_hdrc.debug | USB debug | - | - |

| musb_hdrc.use_dma | USB over network | - | - |

| libertas.libertas_debug | Configure libertas debug | - | - |

| board.ei485 | Enable/disable RS485 | ;Enable RS485 =yes |

;Disable RS485 =no |

| board.modem | Enable/disable GPRS modem | ;Enable modem (IGEPv2 Expansion) =no |

;Enable modem (IGEPv2 Expansion) =yes |

| buddy.revision | Enable hardware buddy revision [A or B] | Only for base0010 =A |

Only for base0010 =B |