Difference between revisions of "DM3730"

From IGEP - ISEE Wiki

Manel Caro (talk | contribs) (→Texas Instruments DM3730) |

Manel Caro (talk | contribs) (→Texas Instruments DM3730) |

||

| Line 4: | Line 4: | ||

'''<u>MPU Subsystem</u>''' | '''<u>MPU Subsystem</u>''' | ||

| − | * [http://downloads.isee.biz/pub/documentation/ | + | * [http://downloads.isee.biz/pub/documentation/DM3730/DM3730,%20DM3725%20Digital%20Media%20Processors%20datasheet%20(Rev.%20D).pdf DM3730] Up to 1-GHz [http://www.arm.com/ ARM] [http://www.arm.com/products/processors/cortex-a/cortex-a8.php Cortex™-A8 Core] ARMv7 Architecture. |

* In-Order, Dual-Issue, Superscalar Microprocessor Core. | * In-Order, Dual-Issue, Superscalar Microprocessor Core. | ||

* [http://www.arm.com/products/processors/technologies/neon.php NEON™ SIMD Coprocessor] | * [http://www.arm.com/products/processors/technologies/neon.php NEON™ SIMD Coprocessor] | ||

| Line 10: | Line 10: | ||

<u>'''High Performance Image, Video, Audio (IVA2.2™) Accelerator Subsystem.'''</u> | <u>'''High Performance Image, Video, Audio (IVA2.2™) Accelerator Subsystem.'''</u> | ||

| − | * | + | * 800-MHz [http://downloads.isee.biz/pub/documentation/OMAP3/TMS320C64x+%20DSP%20Megamodule.pdf TMS320C64x+™ DSP Core] |

* Enhanced Direct Memory Access (EDMA) Controller (128 Independent Channels) | * Enhanced Direct Memory Access (EDMA) Controller (128 Independent Channels) | ||

* Video Hardware Accelerators | * Video Hardware Accelerators | ||

| Line 30: | Line 30: | ||

* Eight Highly Independent Functional Units | * Eight Highly Independent Functional Units | ||

| − | [[File:fbd_sprs685d.png|499x431px | + | [[File:fbd_sprs685d.png|center|499x431px]] |

==Documentation== | ==Documentation== | ||

Revision as of 13:05, 27 February 2018

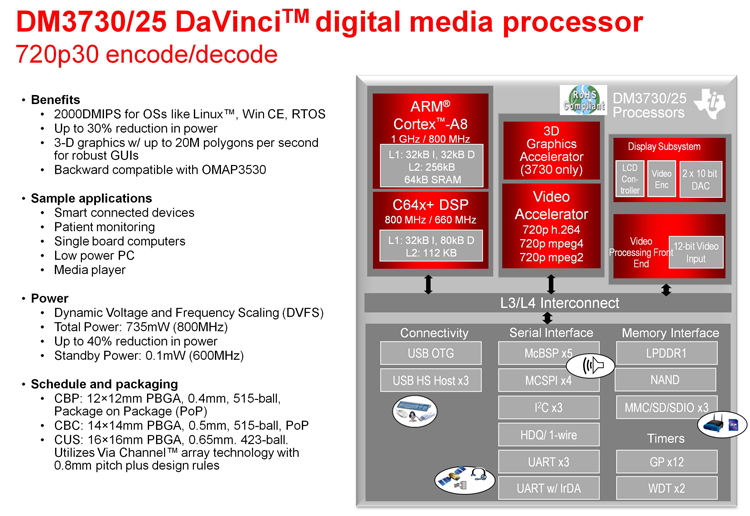

Texas Instruments DM3730

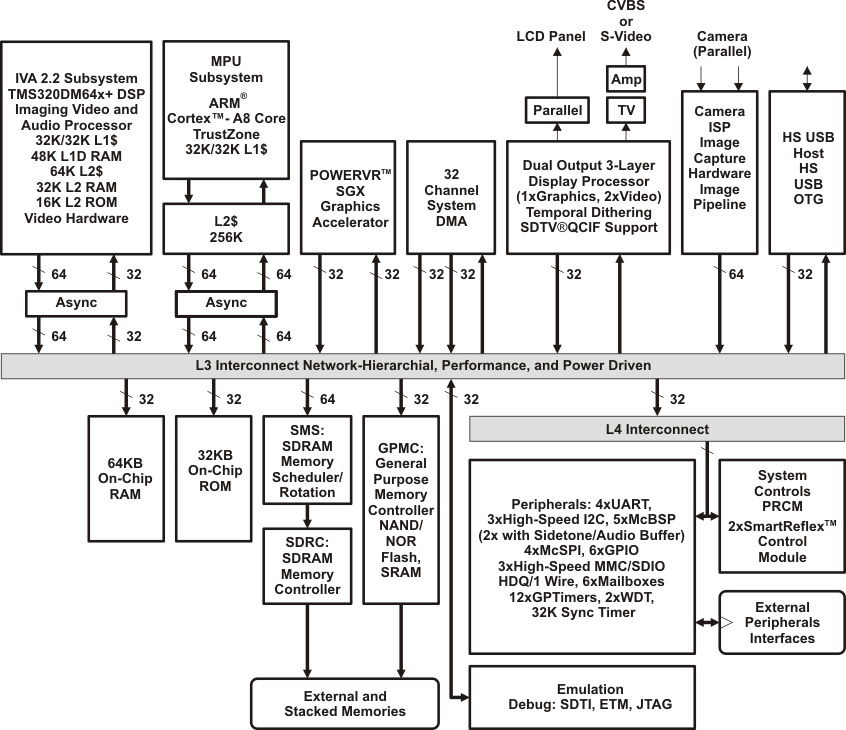

MPU Subsystem

- DM3730 Up to 1-GHz ARM Cortex™-A8 Core ARMv7 Architecture.

- In-Order, Dual-Issue, Superscalar Microprocessor Core.

- NEON™ SIMD Coprocessor

High Performance Image, Video, Audio (IVA2.2™) Accelerator Subsystem.

- 800-MHz TMS320C64x+™ DSP Core

- Enhanced Direct Memory Access (EDMA) Controller (128 Independent Channels)

- Video Hardware Accelerators

POWERVR SGX™ Graphics Accelerator (SGX530 Imagination Technologies)

- Tile Based Architecture delivering 10 MPoly/sec

- Universal Scalable Shader Engine: Multi-threaded Engine Incorporating Pixel and Vertex Shader Functionality

- Industry Standard API Support: OpenGLES 1.1 and 2.0, OpenVG1.0

- Fine Grained Task Switching, Load Balancing, and Power Management

- Programmable High Quality Image Anti-Aliasing

Fully Software-Compatible With C64x and ARM9™

Commercial and Extended Temperature Grades

Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x+™ DSP Core

- Eight Highly Independent Functional Units

Documentation

- OMAP3530 and OMAP3525 Applications Processors datasheet (Rev. H).

- OMAP35x Technical Reference Manual (Rev. Y).pdf

- OMAP35x Peripherals Overview Reference Guide (Rev. A)

- SYS:BIOS (TI-RTOS Kernel) User's Guide (Rev. T)

- TMS320C64x+ DSP Megamodule

- TMS320C64x-C64x+DSP CPU and Instruction set