Difference between revisions of "How to set up UART2 in J990"

From IGEP - ISEE Wiki

| Line 13: | Line 13: | ||

= Fast Mode<br> = | = Fast Mode<br> = | ||

| − | Fast Mode: set up UART2 until system reboot or halt. Using user space to configure mux and disable | + | Fast Mode: set up UART2 until system reboot or halt. Using user space to configure mux and disable bluetooth. Default kernel has disabled TWL4030 PCM voice interface output pins to high impedance, otherwise this module forces the level of mcbsp3_fsx and mcbsp3_clkx pins. To make sure, go to ~/sound/soc/codecs/twl4030.c file already read: <br> |

<pre> 0x04, /* REG_VOICE_IF (0xF) */</pre> | <pre> 0x04, /* REG_VOICE_IF (0xF) */</pre> | ||

=== Configure IGEP === | === Configure IGEP === | ||

| Line 19: | Line 19: | ||

Make sure that IGEPv2 Expansion is disabled, go to igep.ini file: | Make sure that IGEPv2 Expansion is disabled, go to igep.ini file: | ||

<pre>;buddy=igep0022 </pre> | <pre>;buddy=igep0022 </pre> | ||

| − | '''Disable | + | '''Disable Bluetooth:''' |

Log with root user via SSH or Serial cable.<br> | Log with root user via SSH or Serial cable.<br> | ||

| Line 49: | Line 49: | ||

root@localhost:/sys/class/gpio# | root@localhost:/sys/class/gpio# | ||

</pre> | </pre> | ||

| − | '''Disable | + | '''Disable Bluetooth UART2 wires:''' |

Go to /sys/kernel/debug/omap_mux/ | Go to /sys/kernel/debug/omap_mux/ | ||

| Line 102: | Line 102: | ||

signals: mcbsp3_dr | uart2_rts | NA | NA | gpio_141 | hsusb3_tll_data5 | NA | safe_mode | signals: mcbsp3_dr | uart2_rts | NA | NA | gpio_141 | hsusb3_tll_data5 | NA | safe_mode | ||

root@localhost:/sys/kernel/debug/omap_mux# | root@localhost:/sys/kernel/debug/omap_mux# | ||

| − | </pre> | + | </pre> |

| − | |||

=== Test UART2 in J990<br> === | === Test UART2 in J990<br> === | ||

Revision as of 18:48, 25 January 2012

Contents

Overview

This How-To is meant to be a starting point for people to learn to set up UART2 for IGEPv2 J990 connector as quickly and easily as possible. In this how-to, we use Linaro Headless with Kernel 2.6.35.y. This How-To is focused for revisions RC1/RC3/RC4/RC6 (WIFI/BT versions).

More information about UART.

There are two modes to configure UART2 in J990: via user space (fast mode) or editing kernel source and compile it (slow mode).

Feedback and Contributing

At any point, if you see a mistake you can contribute to this How-To.

Fast Mode

Fast Mode: set up UART2 until system reboot or halt. Using user space to configure mux and disable bluetooth. Default kernel has disabled TWL4030 PCM voice interface output pins to high impedance, otherwise this module forces the level of mcbsp3_fsx and mcbsp3_clkx pins. To make sure, go to ~/sound/soc/codecs/twl4030.c file already read:

0x04, /* REG_VOICE_IF (0xF) */

Configure IGEP

Make sure that IGEPv2 Expansion is disabled, go to igep.ini file:

;buddy=igep0022

Disable Bluetooth:

Log with root user via SSH or Serial cable.

Go to /sys/kernel/debug/omap_mux/

Set sdmmc2_dat5 to gpio137 (mode 4):

echo 0x004 > sdmmc2_dat5

Check that:

root@localhost:/sys/kernel/debug/omap_mux# cat sdmmc2_dat5 name: sdmmc2_dat5.gpio_137 (0x48002166/0x136 = 0x0004), b ah3, t NA mode: OMAP_PIN_OUTPUT | OMAP_MUX_MODE4 signals: sdmmc2_dat5 | sdmmc2_dir_dat1 | cam_global_reset | sdmmc3_dat1 | gpio_137 | hsusb3_tll_stp | mm3_rxdp | safe_mode

Go to: /sys/class/gpio/

Check that gpio137 is in user space:

root@localhost:/sys/class/gpio# ls export gpio137 gpio138 gpio139 gpio170 gpio64 gpiochip0 gpiochip128 gpiochip160 gpiochip192 gpiochip32 gpiochip64 gpiochip96 unexport root@localhost:/sys/class/gpio#

If you don't have it, you should export gpio137:

echo 137 > /sys/class/gpio/export

Set gpio137 to low value to disable bluetooth:

echo 0 > /sys/class/gpio/gpio137/value

Check that:

root@localhost:/sys/class/gpio# cat /sys/class/gpio/gpio137/value 0 root@localhost:/sys/class/gpio#

Disable Bluetooth UART2 wires:

Go to /sys/kernel/debug/omap_mux/

Type:

echo 0x007 > uart2_cts echo 0x007 > uart2_rts echo 0x007 > uart2_rx echo 0x007 > uart2_tx

Check that:

root@localhost:/sys/kernel/debug/omap_mux# cat uart2_cts name: uart2_cts.safe_mode (0x48002174/0x144 = 0x0007), b ab26, t NA mode: OMAP_PIN_OUTPUT | OMAP_MUX_MODE7 signals: uart2_cts | mcbsp3_dx | gpt9_pwm_evt | NA | gpio_144 | NA | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux# cat uart2_rts name: uart2_rts.safe_mode (0x48002176/0x146 = 0x0007), b ab25, t NA mode: OMAP_PIN_OUTPUT | OMAP_MUX_MODE7 signals: uart2_rts | mcbsp3_dr | gpt10_pwm_evt | NA | gpio_145 | NA | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux# cat uart2_rx name: uart2_rx.safe_mode (0x4800217a/0x14a = 0x0007), b ad25, t NA mode: OMAP_PIN_OUTPUT | OMAP_MUX_MODE7 signals: uart2_rx | mcbsp3_fsx | gpt8_pwm_evt | NA | gpio_147 | NA | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux# cat uart2_tx name: uart2_tx.safe_mode (0x48002178/0x148 = 0x0007), b aa25, t NA mode: OMAP_PIN_OUTPUT | OMAP_MUX_MODE7 signals: uart2_tx | mcbsp3_clkx | gpt11_pwm_evt | NA | gpio_146 | NA | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux#

Enable UART2 in J990:

Type:

echo 0x101 > mcbsp3_dx echo 0x101 > mcbsp3_clkx echo 0x101 > mcbsp3_fsx echo 0x101 > mcbsp3_dr

Check that:

root@localhost:/sys/kernel/debug/omap_mux# cat mcbsp3_dx name: mcbsp3_dx.uart2_cts (0x4800216c/0x13c = 0x0101), b af6, t NA mode: OMAP_PIN_INPUT | OMAP_MUX_MODE1 signals: mcbsp3_dx | uart2_cts | NA | NA | gpio_140 | hsusb3_tll_data4 | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux# cat mcbsp3_clkx name: mcbsp3_clkx.uart2_tx (0x48002170/0x140 = 0x0101), b af5, t NA mode: OMAP_PIN_INPUT | OMAP_MUX_MODE1 signals: mcbsp3_clkx | uart2_tx | NA | NA | gpio_142 | hsusb3_tll_data6 | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux# cat mcbsp3_fsx name: mcbsp3_fsx.uart2_rx (0x48002172/0x142 = 0x0101), b ae5, t NA mode: OMAP_PIN_INPUT | OMAP_MUX_MODE1 signals: mcbsp3_fsx | uart2_rx | NA | NA | gpio_143 | hsusb3_tll_data7 | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux# cat mcbsp3_dr name: mcbsp3_dr.uart2_rts (0x4800216e/0x13e = 0x0101), b ae6, t NA mode: OMAP_PIN_INPUT | OMAP_MUX_MODE1 signals: mcbsp3_dr | uart2_rts | NA | NA | gpio_141 | hsusb3_tll_data5 | NA | safe_mode root@localhost:/sys/kernel/debug/omap_mux#

Test UART2 in J990

UART2 J990 pins:

| Pin | UART | Wire |

| 4 | UART2_CTS | MCBSP3_DX |

| 6 | UART2_TX | MCBSP3_CLKX |

| 8 | UART2_RX | MCBSP3_FSX |

| 10 | UART2_RTS | MCBSP3_DR |

Test

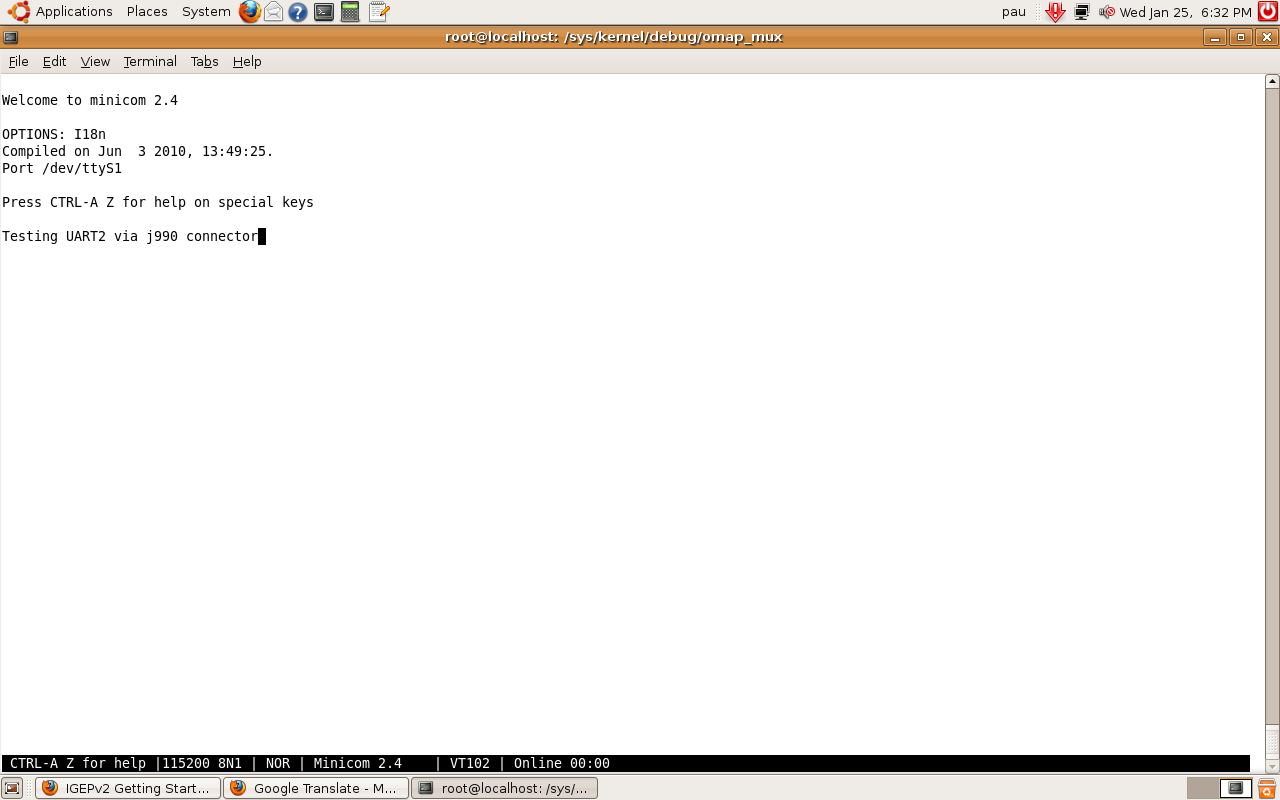

Connect UART2_TX with UART2_RX. Use minicom to prove UART2 (/dev/ttyS1) :

minicom -D /dev/ttyS1

If you write characters and see the echo on the screen, you configure well UART.

|